在近期举行的CadenceLive年度用户大会中,一个核心议题引发了与会工程师、研究者与产业领袖的广泛共鸣:在人工智能浪潮席卷全球的当下,如何借助先进的计算软件工具,系统性、高效率地完成从底层智能芯片设计到上层AI应用软件开发的完整流程,从而加速智能系统的创新与落地。

一、 挑战:AI系统设计的复杂性与“墙”

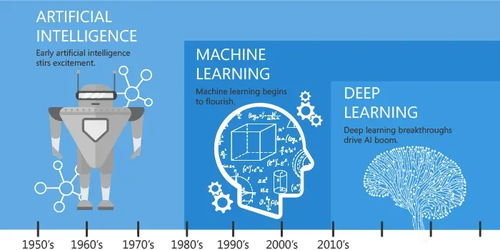

传统电子系统设计已面临摩尔定律放缓、设计规模指数级增长等挑战。而AI时代引入了新的维度:算法、硬件架构与软件栈必须深度融合。开发者面临多堵“墙”:

- 算法与硬件的鸿沟:创新的神经网络模型(如Transformer、扩散模型)需要特定的计算单元(如矩阵乘法单元、稀疏计算加速)和内存层次结构来高效执行。手动进行硬件-算法协同优化耗时且易错。

- 系统级验证的复杂性:智能SoC集成了异构计算核心、高速互连、定制加速器及复杂电源管理,其功能、性能、功耗及可靠性的验证难度呈爆炸式增长。

- 软件开发的滞后:底层硬件的变化要求驱动、编译器、算子库乃至应用框架的同步适配,软件开发往往成为产品上市的瓶颈。

二、 破局:计算软件的全栈赋能

Cadence等EDA(电子设计自动化)与计算软件领导者提出的解决方案,正从传统芯片设计向更广泛的计算系统设计演进,核心在于提供全栈式、数据驱动、高度集成的软件平台。

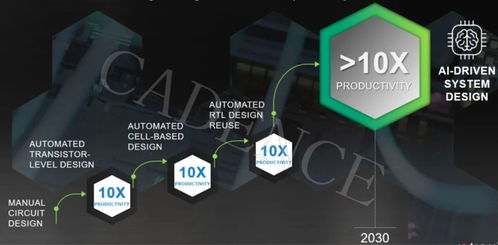

1. 智能芯片与系统设计加速

- AI增强的设计工具:利用机器学习优化布局布线、功耗分析、时序收敛等环节,大幅缩短设计周期。例如,通过预测性模型快速探索设计空间,找到功耗、性能、面积(PPA)的最优解。

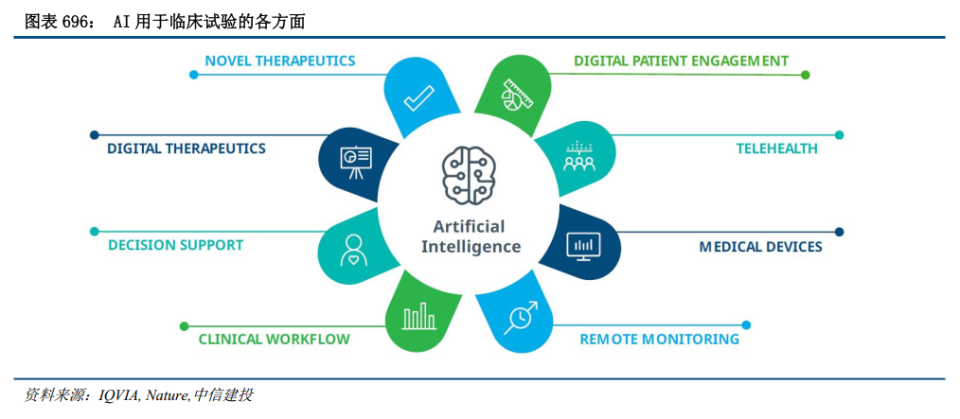

- 系统分析与验证平台:提供从架构探索(如基于虚拟原型的性能建模)、软硬件协同仿真到硅后验证的全套工具。AI技术被用于加速验证收敛,如智能测试生成、故障预测和覆盖率分析。

- 专用IP与加速器设计:提供经过验证的AI/ML处理器IP、高速接口IP以及加速器设计环境,帮助客户快速集成或定制专用计算单元。

2. 驱动AI应用软件开发

这是本次回顾的重点突破方向。计算软件的作用已不止于硬件诞生之后,而是前置并贯穿整个流程:

- 早期软件启动与原型开发:在硬件RTL代码完成甚至流片之前,利用高性能硬件仿真和原型验证系统,为软件开发人员提供一个高精度、可编程的“虚拟硬件”环境。AI应用开发者可以在此平台上提前进行操作系统移植、驱动开发、算法部署和性能剖析,实现“软硬件并行开发”,将软件开发时间提前数月。

- 高效的算法移植与优化:工具链提供从主流AI框架(如TensorFlow, PyTorch)到目标硬件(CPU、GPU、NPU、定制加速器)的编译优化流程。包括自动算子融合、图优化、量化感知训练及混合精度部署,最大化利用硬件算力,简化开发者工作。

- 系统级性能与功耗分析:在统一的数据模型下,软件运行时的性能瓶颈、缓存行为、功耗热点可以与底层硬件设计数据关联分析。这使得软件优化不再是“黑盒”,开发者能清晰地看到代码如何与硬件互动,从而进行针对性优化。

三、 未来展望:构建自我优化的智能系统

演讲与讨论进一步展望了下一代趋势:自主设计系统。通过将AI深度融入设计流程本身,形成闭环:系统在运行中收集数据(性能、功耗、错误),反馈给设计工具,工具据此自动优化后续设计版本或实时调整配置。计算软件平台将成为这一闭环的智能中枢。

结论

CadenceLive的精彩讨论揭示,在人工智能时代,计算软件(涵盖EDA、系统分析、算法开发工具)的角色已从辅助工具演变为智能系统创新的核心引擎与协同平台。通过打破硬件与软件之间的壁垒,提供一个从硅基石到应用顶端的连贯、智能、数据驱动的设计环境,企业和开发者能够以前所未有的速度将AI的想象力转化为现实中的高效、可靠的智能产品,从而在激烈的市场竞争中占据先机。加速智能系统设计,本质上是加速从“想法”到“芯片”再到“用户体验”的整个价值创造流程。